文章编号: 2095-2163(2023)11-0142-06

中图分类号: TN722.77;TN431.1

文献标志码:A

# 一种具有基极补偿技术的高速运算放大器

李洪品1,杨发顺1,2,3,马 奎1,2,3

(1 贵州大学 大数据与信息工程学院, 贵阳 550025;2 贵州大学 半导体功率器件可靠性教育部工程研究中心, 贵阳 550025; 3 贵州大学 贵州省微纳电子与软件技术重点实验室, 贵阳 550025)

摘 要:介绍了一种基于高速互补双极型工艺设计的宽带高速运算放大器。该运放输入级采用折叠式共射-共基结构能够增大输入级带宽,改进型威尔逊电流镜作为有源负载将差分输入信号转换为单端输出信号,并提高输入级差分增益;通过基极补偿技术补偿输入对管基极电流,降低输入偏置电流,提高运放精度。输出级采用双缓冲 AB 类输出级,能够消除交越失真,提高运放带负载能力,并为负载提供较大功率。Spectre 仿真结果表明:在 $\pm$ 15 V,25  $\,^{\circ}$ C,1 k $\Omega$  负载电阻和 10 pF 负载电容条件下输入偏置电流为 34.8 nA,静态电流  $\leq$ 8 mA,单位增益带宽 365 MHz,压摆率 428.1 V/ $\mu$ s,0.01%精度建立时间为 42.3 ns。 **关键词**:运算放大器;高速;宽带;基极电流补偿

# A high-speed operational amplifier with base compensation technology

LI Hongpin  $^1$ , YANG Fashun  $^{1,2,3}$ , MA Kui  $^{1,2,3}$

(1 College of Big Data and Information Engineering, Guizhou University, Guiyang 550025, China; 2 Engineering Research Center of Semiconductor Power Device Reliability, the Ministry of Education, Guizhou University, Guiyang 550025, China; 3 Key Laboratory of Micro-Nano Electronics and Software Technology of Guizhou Province, Guizhou University, Guiyang 550025, China)

**Abstract:** A broadband high speed operational amplifier based on high speed complementary bipolar process design is introduced. The foldable common-base structure of the input stage can increase the bandwidth of the input stage, and taken as an active load, the improved Wilson current mirror can convert the differential input signal into a single-ended output signal, and improve the differential gain of the input stage. Base compensation technology is used to compensate the input base current, reduce the input bias current and improve the accuracy of the operational amplifier. The output stage adopts double buffered Class AB output stage, which can eliminate crossover distortion, improve the load capacity of the op amp, and provide more power for the load. Spectre simulation results show that: The input bias current is 34.8 nA at  $\pm 15$  V, 25 °C, 1 k $\Omega$  load resistance and 10 pF load capacitor. Static current is less than 8 mA, unit gain bandwidth is 365 MHz. The swing rate is 428.1 V/ $\mu$ s, 0.01%. The accuracy establishment time is 42.

Key words: operational amplifier; high speed; wide band; base current compensation

# 0 引 言

作为电子系统的基本单元,集成运算放大器是由多级放大电路直接耦合而成的高增益模拟集成电路,按照不同的需求、应用可以分为多种类型[1]。本设计的电路属于高速运算放大器,一般泛指带宽高于50 MHz 的运放,应用于光学 ToF 系统的高速运放甚至能达到8 GHz。高速运算放大器具有宽

带、高转换速率、低失真和噪声小等突出特点,像ADI、TI等公司甚至能在维持性能的基础上,较大限度地降低电路功耗。目前,高速运放广泛应用于 A/D 和 D/A 转换器、波形发生器和视频放大器以及一些光学应用中。

本文采用了一种高速互补双极工艺。相比于 CMOS 工艺,高速互补双极工艺能为集成电路提供 更大的跨导、更大的增益以及低噪声、低失调等特

基金项目:贵州大学引进人才项目(贵大人基合字(2019)63号);黔科合支撑[2023]一般283。

作者简介: 李洪品(1995-),男,硕士研究生,主要研究方向:模拟集成电路设计; 杨发顺(1976-),男,博士,副教授,硕士生导师,主要研究方向:半导体功率器件与功率集成技术、半导体集成电路设计。

通讯作者: 马 奎(1985-),男,博士,教授,硕士生导师,主要研究方向:半导体集成技术、模拟集成电路设计及应用、半导体芯片的可靠性研究。Email:kma@gzu.edu.cn

收稿日期: 2023-05-23

性;并且该工艺采用 SOI 全介质隔离技术为器件提供高封装密度以及低寄生电容,从而在提升集成度的同时,提高了电路的运行速度。

基于该工艺,本文设计了一款可用于包括视频 监控器、CATV、彩色复印机、图像扫描仪和传真机等 许多高速应用的高速运算放大器。本文的电路采用 的是普通 β 管;因为一般三极管基极电流在微安级 别,在外围电路上产生的压降会增大失调,因此该设 计会采用基极电流补偿技术,使电路满足高速的同 时,也提高了运放的精度。

## 1 电路设计与分析

#### 1.1 高速互补工艺特点

优良的电路结构能够优化并进一步提升电路性能,而工艺则决定了电路的上限。本文所使用的高速互补工艺采用由 SOI 和深槽隔离技术组成的全介质隔离技术:SOI 是一种在绝缘层上生长一层具有一定厚度的单晶硅薄膜材料的技术<sup>[2-3]</sup>,其通过绝缘层实现了器件和衬底的全介质隔离;该技术与传统体硅技术相比具有无闩锁、功耗低、集成度高、耐高温等特点,并且其寄生电容小,因此相比于体硅技术器件,SOI 器件能够有效提高电路运行速度。深槽隔离技术能够增强晶体管的传输特性,降低寄生电容,提高晶体管的高频特性。

综合前文论述的优点,并结合互补双极工艺纵向 NPN 晶体管和 PNP 晶体管性能接近这一特点,该高速工艺有极小的寄生电容,NPN 管与 PNP 管都有很高的特征频率  $f_T$ ,能够在同一功耗的情况下,极大提高整体电路速度并使电路具有很好的高频响应特性。

#### 1.2 高速输入级电路设计

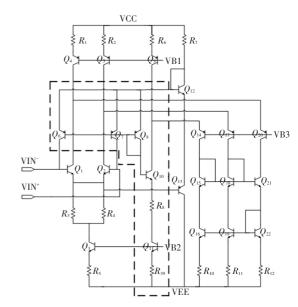

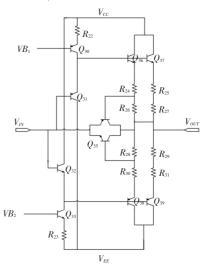

本文介绍输入级电路结构如图 1 所示。

由  $Q_1$ 、 $Q_2$ 、 $Q_{17}$ 、 $Q_{20}$  组成折叠式共射 - 共基串接组态,其有源负载是由  $Q_{18}$ 、 $Q_{21}$ 、 $Q_{19}$ 、 $Q_{22}$  组成的改进型威尔逊电流镜。该结构从折叠点看进去的等效电阻大约为  $1/g_{mP}$ ,则输入管上密勒电倍增效应大概为:

$$C_{M} \approx \left(1 + \frac{g_{mN}}{1 + g_{mN} R_{E}} \cdot \frac{1}{g_{mP}}\right) C_{\mu} \tag{1}$$

其中,  $C_{\mu}$  为输入管上的寄生电容。可以看到该结构大大降低了输入管上密勒效应对带宽带来的影响,并且为增大输入级带宽,输入对管  $Q_1$ 、 $Q_2$  上的寄生应尽可能小。

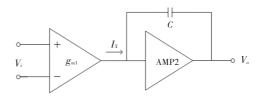

减小输入级等效跨导可以降低频率补偿所要求的电容值。以图 2 所示采用密勒补偿电容的二级运

放为例。

图 1 采用基极补偿技术的输入级

Fig. 1 The input stage with base compensation technology

图 2 采用密勒补偿二级运放

Fig. 2 Two stages op-amp adopting Miller compensation

第一级的等效跨导表达式为:

$$\frac{\Delta I_{X}}{\Delta V_{i}} = g_{m1} \tag{2}$$

第二级高频传递函数约为:

$$\frac{\Delta V_o}{\Delta I_X}(jw) = \frac{1}{jwC} \tag{3}$$

则整个二级运放的传递函数为:

$$\frac{\Delta V_o}{\Delta V_i}(jw) = \frac{g_{m1}}{jwC} \tag{4}$$

假设在 $w_0$ 处传递函数为1,并且电路系统稳定;那么当减小第一级等效跨导时,为维持 $w_0$ 处传递函数依然为1,那么补偿电容也应做相应的减小;并且大信号的响应取决于偏置电流对结点处等效电容的充电速度;因此对于给定的偏置电流在输入对管上增加射极电阻可以使补偿电容所需的容值降低  $[1+(g_{mN}R_E)]$ ,而压摆率将提高 $[1+(g_{mN}R_E)]$ 倍,大大提高了电路对大信号的响应速度;当电路带宽大时,即使在高频信号下电路也依然有很短的建立时间。

因为增大尾电流能够有效增大压摆率,但同时

也会增大运放输入偏置电流;若采用图 3 中的传统基极电流补偿结构,会由于工艺偏差的问题,使得跟随管  $Q_3$ 、 $Q_4$  的  $\beta$  值不会跟  $Q_1$ 、 $Q_2$  完全匹配,并且由于  $Q_5$ 、 $Q_6$  与  $Q_7$ 、 $Q_8$  存在基极电流以及厄尔利效应的影响,使得补偿电流会与  $Q_1$ 、 $Q_2$  的基极电流存在偏差;并且 2 个电流镜结构也无法做到完全对称,因此补偿电流的不对称会极大地增加失调电流。

图 3 传统基极电流补偿结构

Fig. 3 Classical base current compensation structure

综上所述,本文设计了一种基极电流补偿结构来解决上述提到的问题。 $Q_6$ 、 $Q_7$ 、 $Q_8$ 、 $Q_{10}$ 、 $Q_{12}$ 、 $Q_{13}$  组成基极电流消除电路,电路结构见图 1 虚线框。其中, $Q_6$ 、 $Q_7$ 、 $Q_8$ 、 $Q_{10}$  起到基极电流消除的作用, $Q_{12}$ 、 $Q_{13}$  钳住 $Q_{10}$  的基极电位; $Q_{10}$  的基极电位为:

$V_{B10} = V_{IN} - V_{BE12} + |V_{BE13}| + V_{BE12} - |V_{BE8}| \approx V_{IN}$ 为使  $Q_{10}$  的基极电位与  $Q_{1},Q_{2}$  的基极电位相 同,要求  $Q_{10}$  与  $Q_{1}$ 、 $Q_{2}$  匹配, $R_{8}$  与  $R_{3}$  匹配, $Q_{3}$  与  $Q_{11}$ 匹配,  $R_0$  的阻值为 $R_5$  的 2 倍, 分配到 $R_0$  上的电流为  $R_5$  上的一半,则  $Q_{10}$  的发射极电位等于  $Q_1,Q_2$  的发 射极电位,则  $V_{RE10} = V_{RE1}$ ,且皆有相同的基极电流;  $Q_{10}$  管的基极电流通过  $Q_6$  、 $Q_7$  、 $Q_8$  所组成的电流镜结 构,将 $Q_{10}$ 管的基极电流分别送入 $Q_{1}$ 、 $Q_{2}$ 的基极<sup>[4]</sup>, 补偿输入对管的基极电流。相比于2个电流镜结 构,该多输出电流镜的匹配性更佳,避免了补偿电流 不对称的问题。因为厄尔利效应的影响会使  $Q_{10}$  与  $Q_1, Q_2$  的基极电流存在偏差,故要使  $Q_2, Q_{14} \sim Q_{16}$  $R_6$ 、 $R_{10}$  与  $Q_4$ 、 $Q_{20}$  ~  $Q_{22}$ 、 $R_1$ 、 $R_{12}$  匹配,从而使  $Q_{10}$  与  $Q_1, Q_2$  的集电极电位相同, 最终使  $V_{CE10} = V_{CE1} =$  $V_{CE}$ ,消除厄尔利效应的影响。因此,该补偿结构的 对称性要好于传统补偿结构,不会因工艺流程中的 偏差而带来较多的失配。

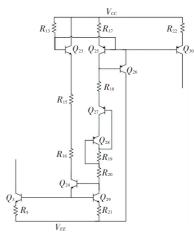

## 1.3 偏置电路设计

偏置电路为整个电路提供基准电流和偏置电 压,使电路能够处于正常的工作状态,其电路结构如 图 4 所示。

图 4 偏置电路

Fig. 4 The bias circuit

图 4 中,  $R_{17} \sim R_{21}$  所在支路上会产生基准电流,并分别通过  $Q_{25}$ 、 $Q_{29}$  按比例分配到  $Q_{3}$ 、 $Q_{30}$  所在支路上。基准电流大小为:

$$I_{\text{REF}} = \frac{V_{CC} + V_{EE} - 5 V_{BE}}{R_{17} + R_{18} + R_{19} + R_{20} + R_{21}}$$

(5)

该偏置电路采用由  $Q_{25}$ 、 $Q_{26}$ 、 $Q_{30}$  和  $Q_{24}$ 、 $Q_3$ 、 $Q_{29}$  组成的  $2 \cap \beta$  – helper 电流镜结构;相比于普通电流镜结构,该结构降低了由晶体管基极电流造成的电流误差,提高了电流镜精度。

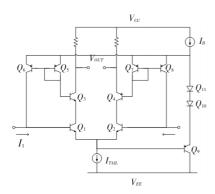

#### 1.4 输出级电路设计

输出级电路主要是由  $Q_{31}$ 、 $Q_{32}$ 、 $Q_{36}$ 、 $Q_{37}$ 、 $Q_{38}$  、 $Q_{39}$  组成的双缓冲 AB 类输出级,电路结构如图 5 所示。其中, $Q_{31}$ 、 $Q_{32}$  的作用类似于二极管:当 VIN 为 0 时, $Q_{36}$ 、 $Q_{37}$  的基极电位为  $V_{BE31}$ , $Q_{38}$ 、 $Q_{39}$  的基极电位为  $V_{BE32}$ ,则此时  $Q_{36}$ 、 $Q_{37}$ 、 $Q_{38}$  、 $Q_{39}$  处于临界导通状态,能够有效避免交越失真的问题。该结构带负载能力强,能够降低前级受到的负载效应,并为负载提供较大功率。

图 5 双缓冲输出级

Fig. 5 The double buffered output stage

输出级电路工作原理:由 KVL 关系得  $V_{BE36,37}$  +  $|V_{BE38,39}|$  =  $V_{BE32}$  +  $|V_{BE31}|$ ; 当输入信号为正时,会降低  $Q_{31}$ 、 $Q_{38,39}$  的 BE 压降,提高  $Q_{32}$ 、 $Q_{36,37}$  的 BE 压降,降低  $Q_{31}$  的导通,提高  $Q_{32}$  的导通,使流入  $Q_{36,37}$  的基极电流增加,而流出  $Q_{38,39}$  的基极电流减少,此时负载上的电流主要取决于流出  $Q_{31}$  的发射极电流;若输入信号持续增加, $Q_{31}$  会截止,而  $Q_{30}$  会进入饱和状态, $Q_{30}$  的电流会全部流进  $Q_{36,37}$ ,此时最大正向输出为:

$V_{OH} \approx V_{CC} - I_{Esat30} R_{22} + V_{CEsat30} - V_{BE36,37}$  (6) 当输入信号为负时则相反,其最大负向输出为:  $V_{OH} \approx -V_{EE} + I_{Esat33} R_{23} - V_{CEsat33} + V_{BE38,39}$  (7) 研究可知,  $Q_{34}$ 、 $Q_{35}$  管为  $Q_{31}$ 、 $Q_{32}$ 、 $Q_{36}$  、 $Q_{37}$  、 $Q_{38}$  、

$Q_{39}$  管提供保护,其工作原理为: 当输出短路到  $V_{cc}$ 时,若输入信号为正时  $Q_{35}$  启动,并将输入强行拉高到 $V_{cc}-I_{C38}$   $R_{28}-|V_{BE35}|\approx V_{cc}-|V_{BE34}|$ ,防止  $Q_{31}$ 、 $Q_{38,39}$  被反向击穿;若短路到 Vee 时  $Q_{34}$  启动,并将输入强行拉低到 $V_{EE}+I_{C36}$   $R_{26}+V_{BE34}\approx V_{EE}+V_{BE34}$ ,防止  $Q_{32}$ 、 $Q_{36,37}$  被反向击穿。短路到地工作原理类似。

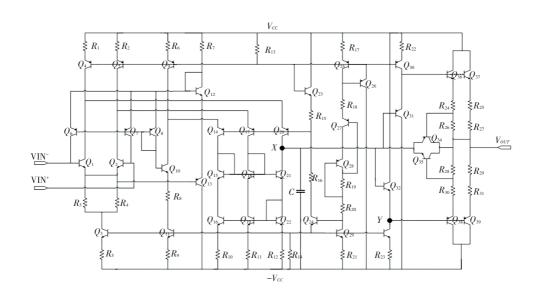

### 1.5 电路频率响应

整体电路结构如图 6 所示。电路总电压增益近似为:

$$A_{v} \approx -\frac{g_{m1}}{1 + g_{m1} R_{3}} \left\{ \frac{\beta_{21} r_{o21}}{2} \| \left[ r_{o20} + \beta_{20} r_{o20} + r_{\pi 20} \| \left( 2 r_{o1} + 2 g_{m1} R_{3} r_{o1} \right) \| \left( r_{o4} + g_{m4} R_{1} r_{o4} \right) \right] \right\}$$

(8)

图 6 整体电路结构

Fig. 6 Overall circuit structure

X 结点处等效电阻非常大,因此该结点处的寄生电容引入的极点就是主极点;在该结点处接上一个较大的电容降低主极点频率,实现主次极点分离,增大相位裕度,使系统更加稳定。主极点可近似为:

$$p_1 \approx -\frac{1}{(C + C_X) R_X} \tag{9}$$

其中,  $R_x$  为输入级电路等效输出电阻,即为电压增益表达式后面的负载项;  $C_x$  为该结点处的等效寄生电容。整体电路压摆率约为:

$$SR = \frac{I_{C3}}{C + C_{Y}} \tag{10}$$

考虑到输出级采用的是功率管,而功率管面积大,相应的寄生也很大,分析可知该点处的时间常数也会很大;因此经过仿真验证,电路次极点在结点 Y处,该处的等效阻抗大约为  $1/g_{m32}$ , 故次极点近

似为:

$$p_2 \approx -\frac{g_{m32}}{C_m} \tag{11}$$

其中,  $C_v$  为该结点处的等效寄生电容。

# 2 性能仿真分析验证

本设计在 Cadence 平台下使用 Spectre 仿真器 对电路进行仿真验证。仿真条件为温度 25  $^{\circ}$  (部分直流特性参数为全温范围)、电源电压±15  $^{\circ}$  V、共模电压 0  $^{\circ}$  V、1  $^{\circ}$  k $^{\circ}$  负载电阻和 10 pF 负载电容。

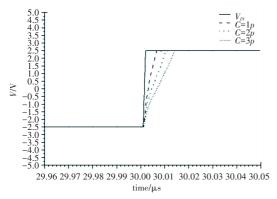

将运放接成电压跟随器的形式,通过改变补偿电容的大小观察其反向端大信号建立的速度,仿真结果如图 7 所示。可以看到当补偿电容在 1p 以下时,其压摆率在 938 V/μs 以上,补偿电容 2p 时、为515.2 V/μs,补偿电容 3p 时、为367.4 V/μs。

图 7 不同补偿电容的大信号响应速度

Fig. 7 Large signal response speed with different compensation capacitors

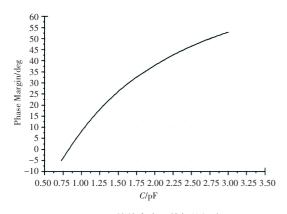

虽然补偿电容较小时,电路有很大的响应速度,但是其相位裕度也会很小,同样带人不同电容值观察电路相位裕度变化,仿真结果如图 8 所示。当补偿电容在 1p 以下时,相位裕度在 8.36 deg 以下,整个闭环系统极其不稳定;当补偿电容在 3p 以上时,此时相位裕度在 53 deg 以上,虽然电路系统此时很稳定,但响应速度也会呈倍数地降低。因此最终做了一个折衷的选择,将补偿电容定在 2.5p,此时相位裕度为 46.66 deg,系统仅会有很小的减幅振荡,压摆率为 428.1 V/µs,0.01%建立时间为 42.3 ns。

图 8 不同补偿电容下的相位裕度

Fig. 8 Phase margin with different compensation capacitors

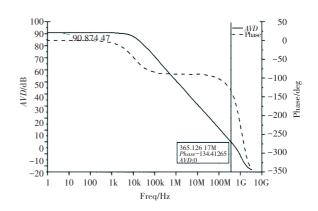

补偿电容为 2.5p 时,运放的开环频率响应特性 仿真 结果 如图 9 所示。运放增益带宽积有 365 MHz,即使得在高频时电路也具有短的建立时间。因此本电路设计符合高速运放的特性。

表1给出了本设计的电路与其他文献电路的性能对比。通过对比可以看出,本设计采用高速互补双极型工艺使得电路能够在较低的电流下获得较大的压摆率和带宽,有效降低了功耗;并且在保持电路性能参数不变的前提下,对晶体管面积做后续优化来降低寄生,则电路静态功耗可以进一步降低。

图 9 开环频率响应仿真结果

Fig. 9 Simulation of open-loop frequency response

表 1 本文电路与其他文献电路性能参数对比

Tab. 1 Performance comparison of circuits between this paper and

references

|        | 开环增益/ | 单位增益   | 压摆率/               | 静态电流/ |

|--------|-------|--------|--------------------|-------|

|        | dB    | 带宽/MHz | $(\sqrt{V/\mu s})$ | mA    |

| 本文     | 90.87 | 365    | 428.1              | 7.5   |

| 文献[9]  | 75    | 51     | 204                | 25.76 |

| 文献[10] | 88.5  | 253.3  | 217                | ≤5.8  |

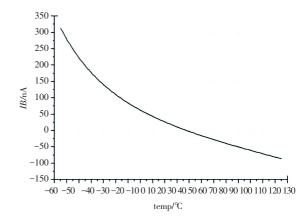

全温范围(-55 ℃ $\sim$ 125 ℃) 直流特性仿真结果 如图 10 所示。

图 10 输入偏置电流仿真结果

Fig. 10 Simulation of input bias current

三极管基极电流通常在 μA 级别,由图 10 看到基极补偿结构可以将输入偏置电流维持在 nA 级别。若对管采用超 β 管或 JFET 管,可将偏置电流降低至 pA 级别;但超 β 管在高频时会使电路不稳定,而 JFET 管温度特性不好,在高温下反向饱和电流会剧增,可能会使输入偏置电流不减反增。因此应视情况选用对管。

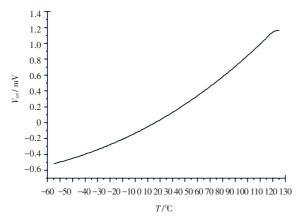

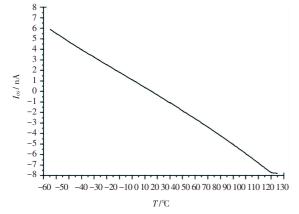

运放失调特性仿真结果如图 11、图 12 所示。 输入级结构不具对称性;因为 2 个共基管的电流不 匹配,使得输入对管的电流不匹配,导致电路产生了 系统失调。虽然有源负载采用的是威尔逊结构,使得两管上的电流具有很高的对称性,但依然会存在一定的误差。假设  $Q_{19}$ 、 $Q_{22}$  完全匹配,且 $I_{C19}$  =  $I_{C22}$ ,则  $Q_{20}$  集电极电流与  $Q_{17}$  集电极电流的关系为:

$$I_{C20} = I_{C17} \left( 1 + \frac{2\beta_{21} - 2\beta_{22} - 2}{2\beta_{22} + \beta_{21} + 2} \right)$$

(12)

$$\varepsilon = \frac{2\beta_{21} - 2\beta_{22} - 2}{2\beta_{22} + \beta_{21} + 2}$$

(13)

上式可看出,纵使  $\beta$  匹配并且很大的情况下依然会存在很小的误差,且受到基区宽度调制效应的影响,  $Q_{21}$  集电极电位和  $Q_{18}$  集电极电位不同也会引入电流镜误差,因此结构仍会存在一定的系统失调。其他重要性能参数见表 2。

图 11 输入失调电压仿真结果

Fig. 11 Simulation of input offset voltage

图 12 输入失调电流仿真结果

Fig. 12 Simulation of input offset current

表 2 部分性能参数

Tab. 2 Partial performance parameters

| 参数     | 符号                   | 仿真结果                    |

|--------|----------------------|-------------------------|

| 共模抑制比  | CMRR                 | 84.32 dB                |

| 电源抑制比  | PSRR                 | 81.51 dB                |

| 输入噪声电压 | $e_n$                | $1.026~\mathrm{nV/VHz}$ |

| 共模输入范围 | CMIR                 | -13.8 V~13.74 V         |

| 输出电压摆幅 | $V_{OL} \sim V_{OH}$ | -13.94 V~13.92 V        |

| 静态电流   | $I_Q$                | 7.5 mA                  |

#### 3 结束语

本文基于高速互补双极工艺设计了一种高速运算放大器。经仿真验证在±15 V,25  $^{\circ}$ C,1 k $\Omega$  负载电阻和 10 pF 负载电容的条件下,得以运放开环增益90.87 dB,相位裕度 46.66 deg,单位增益带宽接365 MHz,压摆率 428.1 V/ $\mu$ s,0.01%精度建立时间为 42.3 ns,静态电流 7.5 mA,输入噪声电压1.026 nV/ $\sqrt{\text{Hz}}$ ,通过采用基极电流补偿技术将运放输入偏置电流降到 34.8 nA,满足高速运算放大器的要求。该运放能够应用于有源滤波器、宽带放大器、ADC 驱动器、视频放大器、缓冲器等应用中。

#### 参考文献

- [1] 宋立范. 集成运算放大器的分类和组成[J]. 考试周刊, 2013 (82):131-132.

- [2] 尤其伟,丁召,马奎. 低噪声视频运算放大器的研究现状及发展趋势[J]. 计算机时代,2022(3):41-44.

- [3] 鲜文佳. 亚微米互补双极工艺关键器件研究[D]. 重庆: 重庆大学, 2010.

- [4] 郭廷. 一种低噪声低失调高精度的运算放大器的研究与设计 [D]. 成都:电子科技大学,2019.

- [5] 任保佳,魏海龙,白欢利. 一种低偏流、低失调的高精度运算放大器设计[J]. 电子设计工程,2022,30(11):163-167.

- [6] 尤其伟. 低噪声视频运算放大器芯片设计[D]. 贵阳:贵州大学,2022.

- [7] 甘明富,冯筱佳,王成鹤. 一种用于视频信号处理的高速宽带运算放大器[J]. 微电子学,2017,47(6):779-783.

- [8] 范国亮. 一种高精度低噪声运算放大器的设计[D]. 成都:电子科技大学,2016.

- [9] 吴世财. 一种八通道高速视频放大器的设计[D]. 西安:西安电子科技大学,2020.

- [10]张镇,王雪原,冯奕. 一种高速高精度 AB 类全差分运算放大器的设计[J]. 电子与封装,2019,19(4):19-23.

- [11] GRAY P R, HURST P J, LEWIS S H, et al. Analysis and design of analog integrated circuits [J]. IEE Review, 1978, 24(7):533.